REVOLUTIONIZING HIGH-POWER

HIGH-TEMPERATURE ELECTRONICS AND

UV OPTOELECTRONICS

CoolCAD Electronics designs and fabricates wide bandgap silicon carbide (SiC) semiconductor transistors and integrated circuits (ICs) for applications in Power Electronics, Green Energy, High-Temperature Electronics and Deep Ultraviolet (UV) Optical Electronics.

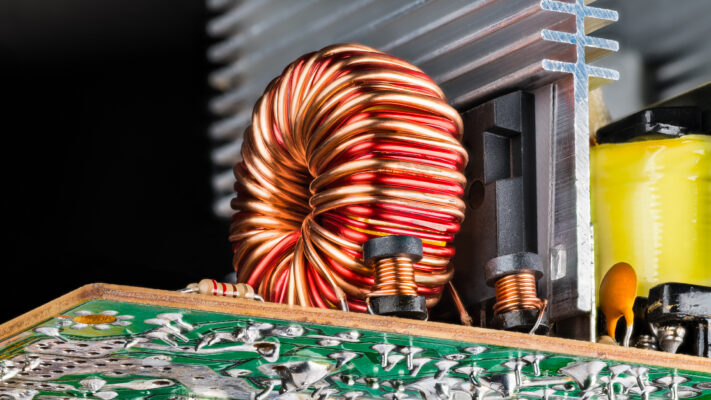

SiC-based semiconductor devices significantly outperform traditional Si (silicon) devices and are a major driver in the transition from an outdated fossil fuel energy infrastructure to a more sustainable infrastructure based on renewable energy technologies.

CoolCAD SiC semiconductor devices operate at temperatures up to and beyond 400°C, that’s significantly above the 200°C capabilities of ordinary silicon-based chips. Our team of scientists and engineers have developed proprietary SiC formulations and manufacturing processes for achieving superior performance with high temperature tolerance.

CoolCAD SiC transistors and ICs are revolutionizing the electronics industry, enabling higher voltage and power applications while reducing system size and weight.

Our Deep Ultraviolet SiC-based optical electronics for UV sensing and imaging function in broad daylight without the need of a special filter required by traditional silicon-based optical sensors.